Undergraduate Research at Jefferson Lab

High-Speed Serial Communication for Data Acquisition

Student: Matthew Stephens

School: College of William and Mary

Mentored By: Hai Dong

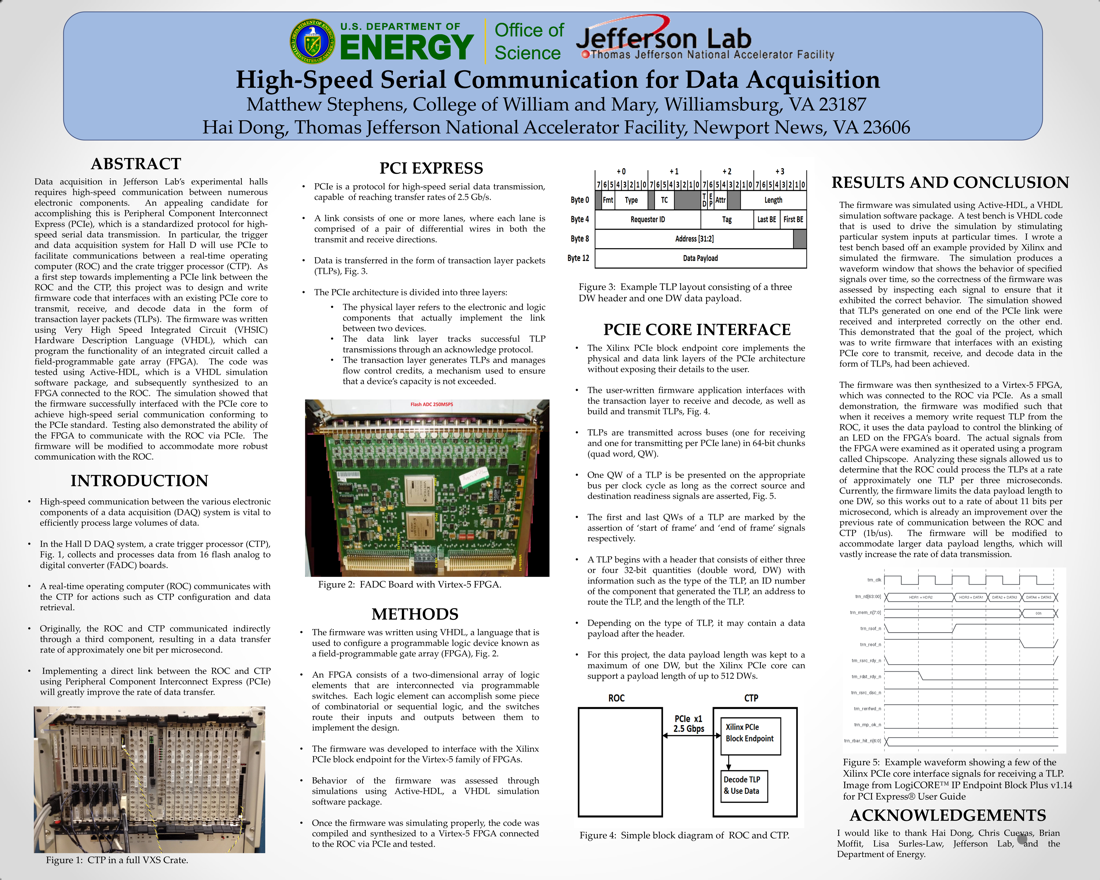

Data acquisition in Jefferson Lab's experimental halls requires high-speed communication between electronic components. An appealing candidate for accomplishing this is Peripheral Component Interconnect Express (PCIe), which is a standardized protocol for high-speed serial data transmission. In particular, the trigger and data acquisition system for Hall D will use PCIe to facilitate communications between a real-time operating computer (ROC) and the crate trigger processor (CTP). This project was to write firmware code that interfaces with an existing PCIe core to transmit, receive, and decode data in the form of transaction layer packets (TLPs). The firmware was written using Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL), which can program the functionality of an integrated circuit called a field-programmable gate array (FPGA). The code was tested using Active-HDL, a VHDL simulation software package, and then synthesized to an FPGA connected to the ROC. Simulation showed that the firmware successfully interfaced with the PCIe core. Testing also demonstrated the ability of the FPGA to communicate with the ROC via PCIe. The firmware will be modified to accommodate more robust communication with the ROC.

Citation and linking information

For questions about this page, please contact Education Web Administrator.